# A 5-GHZ PHASE-LOCKED LOOP USING OVER-SAMPLING FEEDFORWARD PHASE NOISE CANCELLATION

STUDENTS: YI-HSIANG HUANG AND PO-HAO CHENG

#### **Demands for Low-Jitter Sub-6GHz PLL**

#### Wi-Fi 7 (IEEE 802.11be):

- \* Phase noise of LO causes the constellation diagram to rotate.

- → EVM degradation

- Stringent jitter requirement for the required EVM for high-order modulation schemes

- ❖ Ultra-low RMS jitter (~140 fs) is required for 4K-QAM

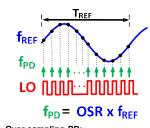

## **Concept of Over-Sampling FFPNC PLLs**

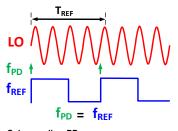

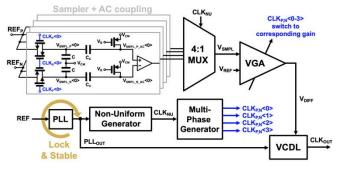

☐ Detect the phase error every reference cycle.

#### Over-sampling PD:

☐ Detect the phase error every PLL cycle. → More frequent detection in one reference

- Jittery PLL<sub>OUT</sub> leads to voltage deviations in the sampled data

- Convert the voltage deviations back into the phase error

- Realign the phase of the PLL<sub>OUT</sub> by Voltage-Controlled Delay Line

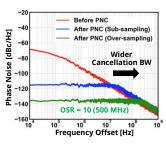

- Break the trade-off between the loop bandwidth and PNC bandwidth

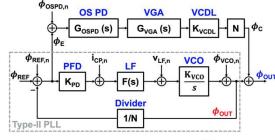

#### Phase Domain System Block Diagram

$$G_{OSPD}(j\omega) = K_{OSPD} \cdot e^{-j\pi \frac{\omega}{OSR \cdot \omega_{REF}}} \cdot \frac{\sin{(\frac{\pi \omega}{OSR \cdot \omega_{REF}})}}{\frac{\pi \omega}{OSR \cdot \omega_{REF}}}$$

$$G_{CAN}(j\omega) = G_{OSPD}(j\omega) \cdot G_{VGA}(j\omega) \cdot K_{VCDL} \cdot N$$

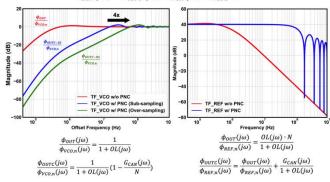

© VCO noise is suppressed by an additional factor

**FUTURE ANALOG SYSTEM TECHNOLOGIES (FAST) LAB**

$\bigcirc$  REF noise directly passes to the  $\phi_{OUTC}$  through the auxiliary path

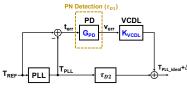

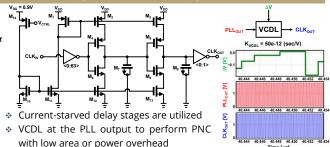

### Voltage-Controlled Delay Line (VCDL)

#### **Proposed Over-Sampling PNC Architecture**

OSR = 4

#### **Future Plan**

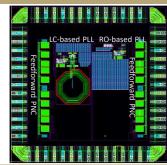

- √ Two Type-II PLLs with different VCOs (LC-based and RO-based).

- Feedforward phase noise cancellation path on each PLL.

- √ TSMC 28nm CMOS process.

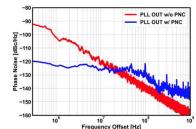

#### **Simulation Results and Conclusions**

- Type II Ring-VCO-Based PLL:

- f<sub>RFF</sub>/ f<sub>PII</sub> = 50 MHz/ 5 GHz

- ❖ PLL loop BW = 500 KHz

- Attain ~20MHz cancellation BW

- RMS iitter = 188 fs

- Phase noise = -123 dBc/Hz at a 1-MHz offset

- ✓ Inherently stable

- Wide-band PNC with a low-frequency REF clock

- Capable of being applied to different frequency bands

**ELECTRICAL & COMPUTER ENGINEERING**